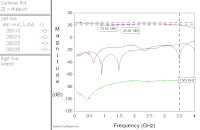

トランジスタ増幅回路の設計と、コンデンサとインダクタによる入出力インピーダンスの整合をシミュレーションで行い、実際に基板を作成して期待通りの性能が出ることを確認しました。

しかし、コンデンサとインダクタで整合をしたので、周波数帯域(一般に減衰量3dBの範囲)はそんなに広くありませんでした。(まあ、当たり前ですが)

このblogでも広帯域アンプなら高周波広帯域増幅用MMIC(Microwave Monolithic IC)だということで、ミニサーキット社のMMICを好んで使用していますが、技術力が落ちていきそうでちょっと心配になってきました。

ここで、ちょっと初心に戻ってトランジスタを使って広帯域アンプを作ってみようかなと思います。

(blogネタ切れなんじゃないか?というつっこみはスルーです)

トランジスタの増幅回路には、エミッタ接地、ベース接地、コレクタ接地など回路がありますが、今回はエミッタ接地回路です。ですが、ちょっと違うのは広帯域アンプを作るために、負帰還を行うということです。負帰還とは、出力の一部を入力に戻してあげることで、これにより全体の出力が一定になります。

この負帰還の増幅回路の帯域幅は、トランジスタのトランジション周波数の10%くらいになります。

さて、高周波トランジスタを用いたRFアンプの設計製作で使ったBFS505という石がまだ余っています。もったいないので、これを使いましょう。この石のトランジション周波数は9GHz程度なので、DC~1GHzくらいの広帯域増幅回路を設計しましょう。

まずいつものとおり、トランジスタ回路で重要なバイアス回路を設計します。下の図は、RFアンプでも出てきた、エミッタ接地回路の基本形です。

ちなみに、抵抗R2はコレクタ電流に対して増幅率hfeがほとんど変化しないようなトランジスタの場合には省略しても大丈夫です。RFアンプの設計製作では、抵抗REも使いませんでした。

とりあえず、この回路のまま使うとして、この回路に負帰還回路を挿入します。コレクタを帰還抵抗RFを通してトランジスタのベースに接続してあげます。また、出力については、トランスをコレクタに接続して、出力信号を外に出してあげます。

下の図は、新たに帰還抵抗RF,RS、バイパスコンデンサC1、C2、C3、トランスT(巻線比N:1)を追加した回路図です。

さて、高い入力インピーダンスを持ち、フィードバックを使う増幅回路といえばオペアンプを思い浮かべますが、実は、上の負帰還増幅回路は簡単なオペアンプの中身を作っているのでした。上のトランジスタ増幅回路をオペアンプ記号に置き換えてみます。

このバイパスをする抵抗を帰還抵抗と呼びます。

では、入力インピーダンスがどのくらいの値になるかというと、帰還抵抗RFをオペアンプのゲインAで割った値となります。

ZIN=RF/A

さて、このオペアンプのゲインAはどのくらいでしょうか?このオペアンプの中身はトランジスタ増幅回路です。一般に、トランジスタ増幅回路のゲインは、増幅率hfeに関わらずエミッタの負荷抵抗RCをコレクタの負荷抵抗REで割った値で求められます。しかし、今回の回路では、交流信号はバイパスコンデンサC2とC3を通るため、抵抗REとRCは通らず、下の図の赤線で囲まれた部分を通ります。

したがって、エミッタの負荷は抵抗RSとなり、コレクタの負荷は、トランスの2次側(巻線比Nの側)の交流負荷となります。このトランスの交流負荷は、出力ポートから見た1次側のインピーダンスをZOUTとすると、その巻線数倍(N倍)となり、N×ZOUTになります。

したがって、ゲインAは、 コレクタの負荷(N×ZOUT)をエミッタの負荷RSで除して

したがって、ゲインAは、 コレクタの負荷(N×ZOUT)をエミッタの負荷RSで除して

A = (N×ZOUT)/RS

となります。 入力インピーダンスの式 ZIN=RF/Aを用いて、Aを消去すれば、

RF×RS = N×ZIN×ZOUT

となりました。 普通は、入出力インピーダンスを50Ωにするので、

RF×RS = N×2500

となります。また、オペアンプの帰還回路のゲインの式、G = (A-1)2をそのまま使って、

G = (RF/50 - 1)2

となります。以上のように、トランジスタ増幅回路に負帰還をさせる場合には、まず交流のゲインを決めます。そして、交流信号が適切に増幅されるような抵抗値を決めます。次に、直流でのバイアス回路で動作点を決めます。適切な動作点での抵抗値が決まったら、直流信号と交流信号では増幅回路の定数が異なるので、バイパスコンデンサを用いて抵抗を分離することで両方に対応することができます。

と、いろいろ書きましたが、抵抗値をどのように決めていくかを実際にやってみないとピンとこないと思いますので、 次回はそれを行います。

応援クリックをお願いします!

|

|

| にほんブログ村 | 電子工作ランキング |